## **GigaDevice Semiconductor Inc.**

# Migration from GD32E5xx to GD32G5xx series

# Application Notes AN218

Revision 1.0

(Jun. 2024)

# **Table of Contents**

| Table  | e of Contents                             |

|--------|-------------------------------------------|

| List o | of Figures                                |

| List o | of Tables4                                |

| 1.     | Foreword5                                 |

| 2.     | Hardware resource comparison6             |

| 3.     | Peripheral and Performance comparison7    |

| 4.     | Differences of peripheral devices9        |

| 4.1.   | On-chip SRAM                              |

| 4.2.   | FMC9                                      |

| 4.3.   | AFIO9                                     |

| 4.4.   | DMA and DMAMUX 10                         |

| 4.5.   | TMU trigonometric function accelerator 10 |

| 4.6.   | ADC 10                                    |

| 4.7.   | DAC 11                                    |

| 4.8.   | IIC 11                                    |

| 4.9.   | SPI 12                                    |

| 4.10   | 0. EXMC 12                                |

| 4.11   | 1. HRTIMER                                |

| 5.     | Revision history13                        |

# **List of Figures**

| Figure 2-1. GD32G5xx and GD32E5xx | pin comparison6 |

|-----------------------------------|-----------------|

# **List of Tables**

| Table 1-1. Applicable products                                                     | . 5 |

|------------------------------------------------------------------------------------|-----|

| Table 3-1. System and peripheral resource comparison between GD32G5xx and GD32E5xx | . 7 |

| Table 4-1. SRAM distribution of GD32G5xx and GD32E5xx                              | . 9 |

| Table 4-2. Flash address distribution of GD32G5xx and GD32E5xx                     | . 9 |

| Table 4-3. ADC differences between GD32G5xx and GD32E5xx                           | 10  |

| Table 4-4. DAC differences between GD32G5xx and GD32E5xx                           | 11  |

| Table 5-1. Revision history                                                        | 13  |

### 1. Foreword

The GD32G5xx series of MCUs is based on the ARM<sup>®</sup> Cortex<sup>®</sup>-M33 processor and represents a new generation of 32-bit general-purpose microcontrollers. Compared to the GD32E5xx series, the GD32G5xx series has seen significant upgrades in terms of product performance, peripheral resources, and functionality. This article primarily introduces these two series of chips from three aspects: hardware resource comparison, peripheral and performance comparison, and peripheral difference comparison, aiming to help developers quickly migrate from GD32E5xx to GD32G5xx, shorten the R&D cycle, and accelerate product development progress.

| Series   | Model number            |

|----------|-------------------------|

| GD32E5xx | GD32E503/E505/E507/E508 |

| GD32E3XX | GD32E513/E515/E517/E518 |

| GD32G5xx | GD32G533/G553           |

#### Table 1-1. Applicable products

#### 2. Hardware resource comparison

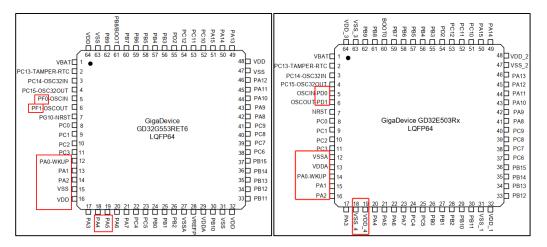

The hardware pin comparison between GD32G5xx and GD32E5xx, taking LQFP64 as an example, is shown in *Figure 2-1 GD32G5xx and GD32E5xx pin comparison*. From this figure, it can be seen that the pin definitions of GD32G5xx are different from those of GD32E5xx. If replacement is needed, users will need to redesign the hardware.

Figure 2-1. GD32G5xx and GD32E5xx pin comparison

<u>Table 2-1 Packaging types and compatibility of GD32G5xx and GD32E5xx</u> presenting the different packaging options for the two chips and the differences among them.

| Packaging types | GD32G5xx     | GD32E5xx     | Compatibility |

|-----------------|--------------|--------------|---------------|

| QFN48           | $\checkmark$ | $\checkmark$ | Incompatible  |

| LQFP48          | $\checkmark$ | $\checkmark$ | Incompatible  |

| LQFP64          | $\checkmark$ | $\checkmark$ | Incompatible  |

| WLCSP81         | $\checkmark$ |              | —             |

| LQFP100         |              | $\checkmark$ | Incompatible  |

| LQFP128         | $\checkmark$ |              | _             |

| LQFP144         |              | $\checkmark$ | _             |

Table 2-1. Packaging types and compatibility of GD32G5xx and GD32E5xx

Note: "  $\checkmark$  " indicates the presence of that type of packaging, "—" indicates no need for it.

## 3. Peripheral and Performance comparison

The GD32G5xx has a richer set of peripheral resources, which can cover the commonly used peripheral resources of the GD32E5xx. The specific system and peripheral resource comparison is shown in <u>Table 3-1 System and peripheral resource comparison between</u> <u>GD32G5xx and GD32E5xx</u>.

| Table 3-1. System | and | peripheral | resource | comparison | between | GD32G5xx | and |

|-------------------|-----|------------|----------|------------|---------|----------|-----|

| GD32E5xx          |     |            |          |            |         |          |     |

| System and peripheral resource | GD32G5xx                                                                       | GD32E5xx                                                  | Remark                             |

|--------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------|

| Clock frequency                | 216MHz                                                                         | 180MHz                                                    |                                    |

| Core                           | M33 (without trustzone)                                                        | M33 (without trustzone)                                   |                                    |

| Flash                          | Up to 512KB dual bank                                                          | Up to 512KB single bank                                   | Incompatible                       |

| SRAM                           | Entire series 128KB                                                            | 96/128KB                                                  | Incompatible                       |

| Power supply range             | 1.71V-3.6V                                                                     | 1.71V-3.6V                                                |                                    |

| Temperature Range              | -40℃~85℃/-40℃<br>~105℃                                                         | -40℃~85℃/-40℃~105℃                                        |                                    |

|                                | Advanced timer *3<br>(16bit)                                                   | Advanced timer *2 (16bit)                                 | Compatible                         |

|                                | GP timer *7 (16bit *5 +<br>32bit *2)                                           | GP timer *10 (16bit *9 +<br>32bit *1)                     | Compatible                         |

| Timer                          | Basic timer *2 (16bit)                                                         | Basic timer *2 (16bit)                                    | Compatible                         |

|                                | High-Precision Timer *1<br>(Maximum resolution<br>144ps)<br>Low-Power Timer *1 | High-Precision Timer *1<br>(Maximum resolution<br>86.8ps) | Partially compatible               |

| U(S)ART                        | USART*3 + UART*2                                                               | USART*4 + UART*2                                          | Compatible                         |

| HRTIMER                        | 1 Master_Timer+<br>8 Slave_Timer                                               | 1 Master_Timer+<br>5 Slave_Timer                          | Compatible                         |

| IIC                            | 4                                                                              | 3                                                         | Partially compatible               |

| SPI                            | 3                                                                              | 3                                                         | Compatible                         |

| SQPI                           | _                                                                              | 1                                                         |                                    |

| QSPI                           | 1                                                                              | _                                                         | Functionality can cover<br>E5 SQPI |

| CAN                            | FD *3                                                                          | FD *3                                                     | Incompatible                       |

| USB                            | _                                                                              | USBFS+USBHS (Internal<br>PHY)                             |                                    |

| SDIO                           | —                                                                              | 1                                                         |                                    |

| Ethernet                       | _                                                                              | 1                                                         |                                    |

| EXMC                           | 1                                                                              | 1                                                         | Partially compatible               |

## AN218 Migration from GD32E5xx to GD32G5xx series

|              | 4 units with 42 external | 3 units with 21 external |                      |

|--------------|--------------------------|--------------------------|----------------------|

| ADC          | channels + 11 internal   | channels + 2 internal    | Partially compatible |

|              | channels                 | channels                 |                      |

| DAC channels | 4                        | 2                        | Partially compatible |

| CAU          | 1                        | —                        |                      |

| TRIGSEL      | 1                        | —                        |                      |

| CLA          | 1                        | —                        |                      |

| TRNG         | 1                        | —                        |                      |

| TMU          | 1                        | 1                        | Compatible           |

| VREF         | 1                        | —                        |                      |

| HDPF         | 1                        | —                        |                      |

| FAC          | 1                        | —                        |                      |

| FFT          | 1                        | —                        |                      |

| CMP          | 8                        | 3                        | Compatible           |

| GPIO         | 107                      | 112                      |                      |

## 4. Differences of peripheral devices

#### 4.1. On-chip SRAM

The maximum SRAM capacity for both GD32G5xx and GD32E5xx is 128KB, but there are differences in the address distribution. For specific details, refer to <u>Table 4-1 SRAM</u> *distribution of GD32G5xx and GD32E5xx*.

| SRAM type | GD32G5xx                         | GD32E5xx                         |

|-----------|----------------------------------|----------------------------------|

| SRAM0     | 0x2000 0000 – 0x2001 3FFF (80KB) | 0x2000 0000 - 0x2001FFFF (128KB) |

| SRAM1     | 0x2000 4000 – 0x2001 7FFF (16KB) | _                                |

| TCMSRAM   | 0x1000 0000 – 0x1000 7FFF (32KB) | _                                |

Table 4-1. SRAM distribution of GD32G5xx and GD32E5xx

Additionally, the SRAM in GD32G5xx features ECC functionality, supporting 1-bit error correction and multi-bit error detection, while the SRAM in GD32E5xx does not include ECC functionality.

#### 4.2. FMC

The maximum Flash size for both GD32G5xx and GD32E5xx is 512KB. The difference is that E5xx has a single Bank with a flash page size of 8KB; whereas G5xx can be configured for single/double Bank operation. In single Bank mode, the flash page size is 1KB, which means that the code running in another Bank will not be blocked while erasing or writing Flash. In double Bank mode, the flash page size is 2KB. For specific details, refer to <u>Table 4-2 Flash</u> address distribution of GD32G5xx and GD32E5xx.

Table 4-2. Flash address distribution of GD32G5xx and GD32E5xx

| SRAM type | GD32G5xx                         | GD32E5xx                         |

|-----------|----------------------------------|----------------------------------|

| SRAM0     | 0x2000 0000 – 0x2001 3FFF (80KB) | 0x2000 0000 - 0x2001FFFF (128KB) |

| SRAM1     | 0x2000 4000 – 0x2001 7FFF (16KB) | —                                |

| TCMSRAM   | 0x1000 0000 – 0x1000 7FFF (32KB) | _                                |

#### 4.3. AFIO

The AF capabilities of the I/O ports on GD32E5xx are relatively fixed, whereas on GD32G5xx, the AF capabilities of the I/O ports are selected through AF numbers, which reduces the likelihood of conflicts between I/O ports.

#### 4.4. DMA and DMAMUX

GD32E5xx is equipped with two DMA controllers, where DMA0 has 7 channels and DMA1 has 5 channels, with each DMA channel being tied to specific peripheral trigger conditions. In contrast, GD32G5xx also has two DMA controllers, with DMA0 having 7 channels and DMA1 having 7 channels. Additionally, GD32G5xx introduces a DMAMUX, which enables any DMA channel to select any peripheral trigger condition, greatly increasing the flexibility of the DMA system.

#### 4.5. TMU trigonometric function accelerator

GD32E5xx has a TMU with 9 modes, and it only supports the IEEE-754 32-bit single-precision floating-point format for operational data. GD32G5xx, on the other hand, has a TMU with 10 modes (supporting more complex operations), and it supports both q1.31 and q1.15 fixed-point formats as well as the IEEE754 32-bit single-precision floating-point format for operational data.

#### 4.6. ADC

The differences in the ADC between the two chips are detailed in <u>Table 4-3 ADC differences</u> <u>between GD32G5xx and GD32E5xx</u>.

| ADC<br>differences                    | GD32G5xx                                                                                                                        | GD32E5xx                                                                |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Number of ADC                         | 4                                                                                                                               | 3                                                                       |

| Number of channels ADC                | ADC0: 14 external+5 internal<br>ADC1: 16 external +3 internal<br>ADC2: 15 external +5 internal<br>ADC3: 18 external +3 internal | ADC0: 16 external +2 internal<br>ADC1: 16 external<br>ADC2: 13 external |

| Number of IOs<br>available for<br>ADC | 42                                                                                                                              | 21                                                                      |

| External trigger sources for ADC      | Configured with TRIGSEL with greater<br>flexibility                                                                             | ADC has a fixed number of trigger sources, which is quite restrictive   |

| Reference<br>source                   | External voltage reference source or<br>internal reference source                                                               | External voltage reference source                                       |

| Internal<br>channels                  | Temperature sensor<br>High-precision temperature sensor<br>Vrefint                                                              | Temperature sensor<br>Vrefint                                           |

#### Table 4-3. ADC differences between GD32G5xx and GD32E5xx

|                 | Battery voltage detection channel                                     |                                       |

|-----------------|-----------------------------------------------------------------------|---------------------------------------|

|                 | DAC_OUT channel                                                       |                                       |

| ADC             | Supports synchronization of two ADCs<br>(ADC0 and ADC1) or three ADCs | Only supports synchronization of ADC0 |

| synchronization | (ADC0, 1, 2)                                                          | and ADC1                              |

#### 4.7. DAC

The differences in DAC between the two chips are shown in <u>Table 4-4 DAC differences</u> <u>between GD32G5xx and GD32E5xx</u>.

| DAC difference       | GD32G5xx                             | GD32E5xx                                          |  |

|----------------------|--------------------------------------|---------------------------------------------------|--|

| items                | 00020077                             | ODGELGAA                                          |  |

| Number of DAC        | 4                                    | 1                                                 |  |

|                      | DAC0: 2 external                     |                                                   |  |

| Number of DAC        | DAC1: 2 external                     | DAC: 2 external                                   |  |

| channels             | DAC2: 2 internal                     |                                                   |  |

|                      | DAC3: 2 internal                     |                                                   |  |

| Number of IOs        |                                      |                                                   |  |

| available for        | 4                                    | 2                                                 |  |

| DAC                  |                                      |                                                   |  |

| External trigger     | Configured with TRIGSEL with greater | The DAC has a fixed number of trigger             |  |

| sources for DAC      | flexibility                          | sources, which is quite restrictive               |  |

| Reference            | External voltage reference source or | External voltage reference source                 |  |

| source               | internal reference source            |                                                   |  |

|                      | Temperature sensor                   |                                                   |  |

| Internal<br>channels | High-precision temperature sensor    | Temperature sensor                                |  |

|                      | Vrefint                              |                                                   |  |

|                      | Battery voltage detection channel    | Vrefint                                           |  |

|                      | DAC_OUT channel                      |                                                   |  |

| 4.00                 | Supports synchronization of two ADCs |                                                   |  |

| ADC                  | (ADC0 and ADC1) or three ADCs        | Only supports synchronization of ADC0<br>and ADC1 |  |

| synchronization      | (ADC0, 1, 2)                         |                                                   |  |

#### 4.8. IIC

The GD32E5xx features 3 IIC interfaces, and the GD32G5xx has 4 IIC interfaces. Specifically, the GD32E5xx is categorized into two types of IIC, with IIC0 and IIC1 being Type I, and IIC2 being Type II; all 4 IIC interfaces of the GD32G5xx are Type II.

#### 4.9. SPI

The GD32E5xx series SPI supports 8-bit or 16-bit data frame formats, and the GD32G5xx SPI supports data frame formats from 4 to 16 bits.

#### 4.10. EXMC

The GD32E5xx EXMC supports access to external media such as: SRAM, ROM, NOR Flash, NAND Flash, PC cards; the GD32G5xx supports: SRAM, ROM, NOR Flash, PSRAM.

#### 4.11. HRTIMER

The differences in HRTIMER between the two chips are shown in <u>Table 4-5 Differences in</u> <u>HRTIMER between GD32G5xx and GD32E5xx</u>.

| HRTIMER            | GD32G5xx                                  | GD32E5xx                              |

|--------------------|-------------------------------------------|---------------------------------------|

| difference items   | GD32G3XX                                  |                                       |

| Number of          | 0                                         | 5                                     |

| Slave_Timer        | 8                                         |                                       |

| Number of channels | Up to 16 channels or up to 8              | Up to 10 channels or up to 5          |

|                    | complementary pairs.                      | complementary pairs.                  |

| fhrtimer_pscck     | Maximum:                                  | Maximum:                              |

|                    | f <sub>clk</sub> *64/2 = 216M*64/2=6.912G | f <sub>clk</sub> *64 = 180M*64=11.52G |

| Table 4-5. Differences in | HRTIMER between | GD32G5xx and GD32E5xx |

|---------------------------|-----------------|-----------------------|

|                           |                 |                       |

## 5. Revision history

#### Table 5-1. Revision history

| Revision No. | Description     | Date        |

|--------------|-----------------|-------------|

| 1.0          | Initial release | Jun.8, 2024 |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2024 GigaDevice - All rights reserved